# HIGH-SPEED DIGITAL SIGNAL PROCESSING PLATFORM

## **AT A GLANCE**

Versatile, high-end platform for real-time testing of digital signal processing algorithms. Based on the Micro-TCA standard, supporting various plug-in boards (ADC, DAC, 100G-Interfaces, FPGA processors)

### Features

ECCEPTE 2 bit ADC and CECEPTE

- 56 GSa/s, 8-bit ADC and 65 GSa/s, 8-bit DAC plug-in boards with real-time data interface

- Multiple ADC/DAC boards can be combined in one platform, to generate synchronized multi-channel (1 to 16) ADCs and DACs

- Free-programmable internal Virtex Ultrascale/Ultrascale+

FPGA plugin boards

- High-speed interfacing between boards within the platform and to external FPGA boards

- Platform supports third party modules based on Micro-TCA standard

- Built-in Gigabit Ethernet (GbE) service interface with FPGA access

- Ready-to-use IP cores for hardware interfacing and reference real-time DSP functions available

### Applications

- Test of DSP algorithms in real time

- Online transmission performance evaluation of coherent optical transmission systems

- Online measurement and debugging

- Prototyping of FPGA-based real-time transceivers

#### Datasheet

|                                               | DSPP 114x<br>plug-in board                         | DSPP 124x<br>plug-in board                         | DSPP 144x<br>plug-in board      | DSPP 154x<br>plug-in board             |

|-----------------------------------------------|----------------------------------------------------|----------------------------------------------------|---------------------------------|----------------------------------------|

| Type of board                                 | Digital-to-Analog<br>Converter                     | Analog-to-Digital<br>Converter                     | FPGA Processor                  | Electro-Optical<br>Front-End           |

| Number of channels per board                  | 1x Full-Rate Analog Out<br>2x Half-Rate Analog Out | 2x Full-Rate Analog Out<br>4x Half-Rate Analog Out | 5 x 100G (QSFP28)               | 4 x Analog In/Out<br>1x Optical In/Out |

| Full rate<br>per channel                      | 54-65 GSa/s                                        | 56 GSa/s                                           | -                               | Up to 32 GBd                           |

| Nominal resolution                            | 8 bit                                              | 8 bit                                              | -                               | -                                      |

| Analog 3dB-<br>bandwidth                      | 15 GHz                                             | 15 GHz                                             | -                               | > 15 GHz                               |

| Internal FPGAs                                | Virtex Ultrascale<br>(XCVU190)                     | Virtex Ultrascale<br>(XCVU190)                     | Virtex Ultrascale+<br>(XCVU13P) | -                                      |

| Total available<br>CLB LUTs                   | 1,074,240                                          | 1,074,240                                          | 1,728,000                       | -                                      |

| Total available<br>CLB Flip-flops             | 2,148,480                                          | 2,148,480                                          | 3,456,000                       | -                                      |

| Total available<br>Block RAMs<br>(36 Kb each) | 3,780                                              | 3,780                                              | 2,625 + 10,000<br>UltraRAM      | -                                      |

| Total available<br>DSP slices                 | 1,800                                              | 1,800                                              | 12,288                          | -                                      |

| Backplane<br>Interface speed                  | up to 2560 Gb/s                                    | up to 560 Gb/s                                     | up to 1120 Gb/s                 | -                                      |

| Front plate<br>connector type                 | GPPO/SMPM                                          | GPPO/SMPM                                          | QSFP28                          | GPPO/SMPM<br>LC optical                |

Dr.-Ing. Robert Elschner Photonic Networks and Systems

Phone +49 30 31002-414 products-pn@hhi.fraunhofer.de

Fraunhofer Heinrich Hertz Institute Einsteinufer 37, 10587 Berlin Germany

www.hhi.fraunhofer.de/dsp-platform

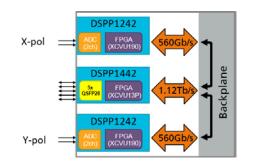

Example setup of High-Speed Digital Signal Processing Platform in Receiver Configuration constraints and the second sec

© Fraunhofer Heinrich Hertz Institute, Berlin 2018